数字EDA研究之Yosys简介

数字EDA研究之Yosys简介

HDL逻辑综合工具Yosys简介

此文是个人对英文网站 的翻译。

1. 什么是Yosys?

Yosys最初来自于Claire Wolf的理学学士论文项目,旨在支持一种CGRA(粗粒度可重用架构)的综合。后来,它扩展成为数字电路逻辑综合研究的一种基础工具。

它提供了对Verilog 2005的可综合的子集的完全支持。人们把它描述为“硬件综合领域的GCC",得益于开源,它的使用者包括来自业余研究/商业应用/学术界的人员。

osys在ISC许可证下发布:

ISC许可证允许人们对采用ISC源代码做任何事情,但没有保证。ISC许可证在功能上等同于BSD 2-Clause和MIT许可证,删除了一些不再需要的语言。

与布局布线工具nextpnr一起,Yosys可用于完全端到端开源流程工具(Lattice iCE 40和ECP 5)的FPGA编程。它还是OpenLane软件的综合部分,其目标是SkyWater 130nm开源PDK,用于完全开源的ASIC设计。Yosys还可以使用后端对求解器格式(如SMT2)进行正式验证。

2 它能做什么?

- 读取和处理verilog 2005语言描述代码

- 在网表(RTL,逻辑,门)上执行各种操作

- 使用ABC,完成逻辑优化和门映射

2.1 典型应用

- 最终生产设计的综合

- 预生产综合(在投资其他生产工具前试运行)

- 从完全特征的verilog到简单verilog的转换

- verilog到其他格式(BLIF,BTOR等)的转换

- 验证综合算法(例如教育用途)

- 新算法实验框架

- 用于构建自定义流程的框架(不局限于逻辑综合,还包括形式验证、逆向工程等)

2.2 不能做什么

- 处理高阶语言(如C/C++/SystemC)

- 创建物理版图(布局与布线)

- 和nextpnr结合可以做到这一点。

3 Yosys套件

不仅包括Yosys本身,还包括围绕它而构建断一系列工具:

SBY :用于形式化验证

Yosys提供输入解析和转换为求解器引擎使用的格式。Yosys还提供了一个统一的验证框架,用于为本机不支持的引擎提供全轨迹跟踪和反例。SBY源|SBY文档

EQY:等价性检查

除了输入解析和准备之外,Yosys还提供了插件支持,使EQY能够直接对设计进行操作。

MCY:互斥覆盖率

SCY

由于SCY生成并运行SBY,Yosys为SCY提供了与SBY相同的实用程序。Yosys还提供输出深度跟踪所需的跟踪连接。

4 原始论文摘要

Yosys文档的第一个版本是作为维也纳科技大学的学士论文发表的

摘要:

今天的大多数数字设计都是在HDL代码(主要是Verilog或VHDL)和HDL综合工具的帮助下完成的。

在特殊情况下,例如粗粒度单元库的综合或测试新的综合算法时,可能需要编写自定义HDL综合工具或向现有工具添加新功能。在这些情况下,提供一个自由和开放源码软件综合工具,作为定制工具的基础,将是有益的。

在没有这样一个工具的情况下,开发了Yosys开源综合套件(Yosys)。本文档涵盖了该工具的设计和实现。目前,Yosys的主要重点在于数字综合的高级方面。Yosys使用现有的开源逻辑综合工具ABC来执行高级门级优化。

包括基于真实世界设计的Yosys评估。结果表明,Yosys可以用来综合这样的设计。对Yosys在该测试中产生的结果使用了形式化验证,证明结果是正确的,并且在质量上与商业综合工具产生的结果相当。

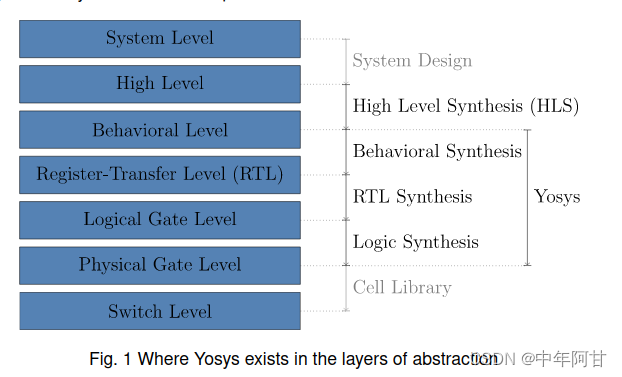

Yosys是一种逻辑综合工具,它的输入是行为级电路设计描述,输出是电路设计的RTL/门级/开关级描述。Yosys中存在涉及范围很广的命令(综合通道),可用于在行为、rtl和逻辑综合领域内执行广泛的综合任务。

4 开源HDL综合器的好处

成本

重用性和可复现性

框架

Yosys不仅仅是一个工具。它是一个可以作为其他开发基础的框架,因此研究人员和黑客都不需要重新发明基本功能。可扩展性是Yosys的设计目标之一。

一站式

由于Yosys的框架特性,越来越多的功能可以在一个工具中使用。Yosys不仅可以用于电路综合,还可以用于形式等价检查,SAT求解和电路分析,仅举几个其他应用领域。对于专有软件,人们需要为这些应用程序中的每一个学习新的工具。

教育工具

专有的综合工具有时对它们的内部工作非常保密。它们通常是黑盒子。Yosys对其内部结构非常开放,很容易观察到综合的不同步骤。

5 Yosys的历史

硬件描述语言(HDL)是一种描述电路的计算机语言。Yosys把电路的HDL描述作为输入,把能够实现给定电路的网表作为输出。

目前最广泛使用和支持的数字电路HDL是Verilog和VHDL。这两种HDL都能用于测试和验证目的以及逻辑综合,从而产生一组可综合和一组不可综合的语言功能。Yosys只关注语言特征的可综合子集。

在最近的异构粗粒度可重构逻辑的工作中,出现了对定制的特定于应用的HDL综合工具的需求。人们很快意识到,理解Verilog或VHDL的综合工具将优于定制HDL的综合工具。给定一个现有的Verilog或VHDL前端,编写必要的附加功能并将其集成到现有工具中的工作可以估计与编写一个支持最小化自定义HDL的新工具大致相同。

拟议的定制HDL综合工具应根据自由和开放源码软件许可证获得许可。因此,需要现有的遵循开源许可的 Verilog或VHDL综合工具作为基础。选择Verilog或VHDL的主要优点是能够综合现有的HDL代码,并减轻电路设计人员学习新语言的要求。为了充分利用任何现有的自由和开放源码软件Verilog或VHDL工具,这种工具必须提供可综合的HDL子集的功能完整的实现。

基本RTL综合是一个很好理解的领域。计算机语言的词法、语法分析和处理是一个深入研究的领域。编写这些工具所需的所有信息已经公开了很长时间,因此很可能必须存在一个具有功能完整的Verilog或VHDL前端的开源HDL综合工具,它可以用作定制RTL综合工具的基础。

由于作者对Verilog的偏好超过了VHDL,因此很早就决定使用Verilog而不是VHDL [1]。对现有的开源Verilog综合工具进行了评价。这次评估的结果是完全毁灭性的。因此,实现了一个全新的Verilog综合工具,并推荐作为自定义综合工具的基础。这是本文档中讨论的工具。

参考文献

A quick investigation into FOSS VHDL tools yielded similar grim results for FOSS VHDL synthesis tools.