DFT-对芯片测试的理解二-详解

DFT - 对芯片测试的理解(二) 详解

DFT - 对芯片测试的理解(二) 详解

参考:

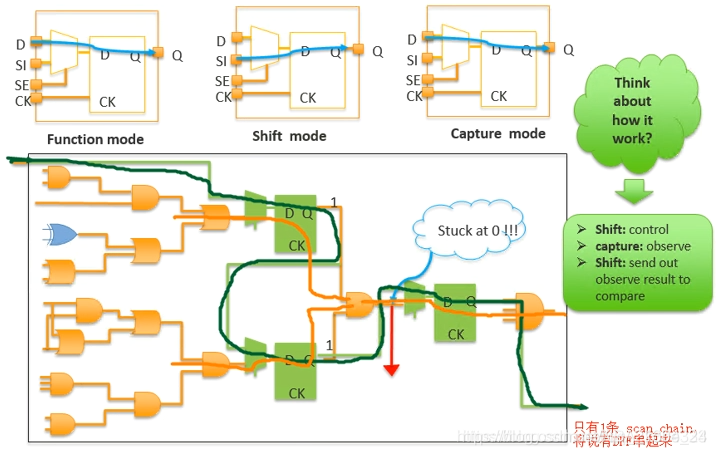

The basic view of DFT scan chain

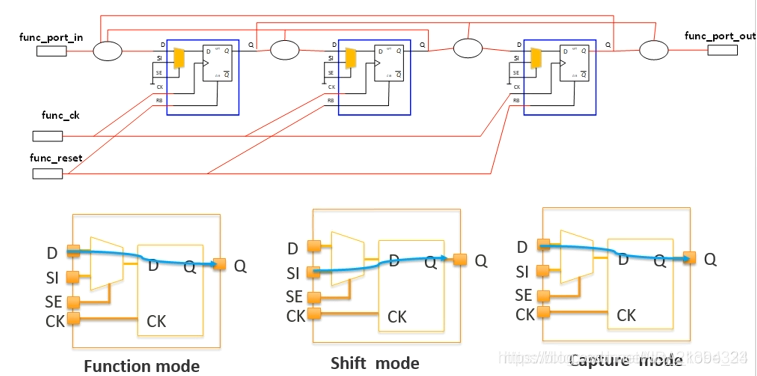

这图很好的理解,Pre DFT时,将 DFF 换成 scan-FF ,让电路具备三种模式的切换。

Function mode:即chip正常的工作模式。此时SE=0。

Shift mode: 此时SE=1,选择Scan模式,并注入期望的SI序列,这样可以让每个 scan cell 有一个确定的值。

然后切换回function mode,从D输入期望的序列,与原来cell中的值运算,得到一些特定的输出。

Capture mode:在pulse clk下依次移出cell中的值,在输出捕获,进行检测。

注:其中椭圆为组合逻辑,如与或非门。

[参考资料:]

( )

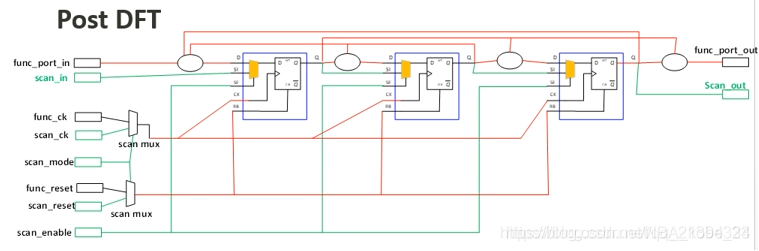

上图看到,在post阶段,和pre对比,有以下不同:

- Pre时,SI和SE均接0;Post后,接入外部测试信号 scan_in和 scan_enable ,并且对clk也增加了 scan_ck/scan_rst 和 scan_mode(scan_mux)。作用在于连接整个scan-FF,以形成 scan_chain。其中 scan_in的连接要特别注意,如图,当选择 SI信号时,它们都是在上一级DFF的Q端输出且不经过组合逻辑的信号。即可预测,在scan_mode下,过DFF的SI值都不经过comb,它们是确定的scan_in信号,只在clk下shift更新值。即scan_in输入什么序列,它们就是什么序列,不会被组合电路改变。同样,scan_out也是不经过comb直接在最后一个DFF输出。

这个方法,便能保证在scan_mode时,每个cell(内部节点)上都有确定的值。

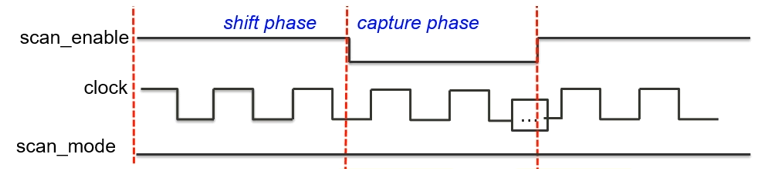

shift与capture mode

先SE=1,通过SI进行shift;在SE=0,切换到D,在scan_out进行capture。由scan_mode控制ck和rst的设置。

//理解其中测试的巧妙之处。

–> 通过scan_chain可以控制每个scan-FF的值,以在capture阶段得到一定规律的序列。实际测试序列和Tool计算的序列对比,如果不对,则可以发现错误。并可以根据多个错误的组合,找到缺陷的具体地方。

其中,需要测试pattern,按照特定规律的激励序列进行测试,就能完成强大的测试。

Fault kinds 缺陷类型。

Stuck-At Fault Model 栓到0和1的情况。Stuck-0,指该点被贴0,不能变化到1。

Poor controllability and observability

可控性和可观测性差。若直接功能测试,在门级电路和寄存器很多时,很难监测这个故障。

因此,增加另外的路径,专用于控制和监测,即DFT。– 每个DFF前插入MUX,多的一端直接有SI输入确定信号,不经过任何组合(逻辑门)电路。便可以在特定点,得到确定的值(shift),然后用确定值来测试后一级的组合逻辑功能是否正确。即后一级的组合逻辑是否能0/1正常变化等。后一级经过DFF之后,也要不通过组合逻辑就输出,进行capture。

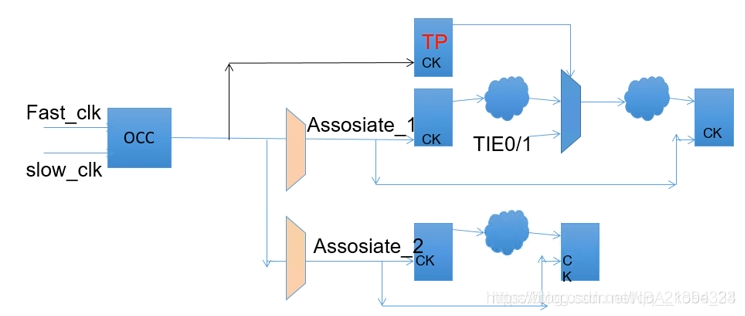

从上图分析DFT是怎样工作的,可以看到:

- 在scan_mode 下,所有的DFF都被串成了一条链路,即scan_chain(绿色部分)。他们中间没有任何comb干扰,即“跃过”comb,形成单纯的DFF链。– 这样做的好处是,就可以shift到每个Cell(DFF模块)一个确定的值了。

- 在capture模式,是SI和PI信号经过comb之后的结果。– 其中怎么来分析结果,就是我一直想弄明白的。

- 还有 scan_ck 是用于在观测时,逐个输出结果,方便ATE去捕获。

cell和DFF的关联与区别:

cell 可以是一个module,可以是多个DFF和组合电路组成的模块。以外部PIN为终点。

DFF仅是D->Q的触发器,时钟沿触发,更新输出。

☆ Tool会自动在每个DFF(flip flop)之间插入mux,添加scan功能。为什么是在每个DFF之间呢?

我们回到DFT的本源目的:“为了检测芯片的物理缺陷,在某些地方插入一些可观测的寄存器”。直接插寄存器,即DFF,那肯定不行,这样消耗资源太多了。因此,采用“改造”原本芯片中就存在的DFF,增加MUX选择的方式,来增加测试点,实现观测芯片内部关键点的功能。

那我们要问了,这样做只能观测DFF存在的地方,那一些组合逻辑很大的地方,岂不是就测试不了?

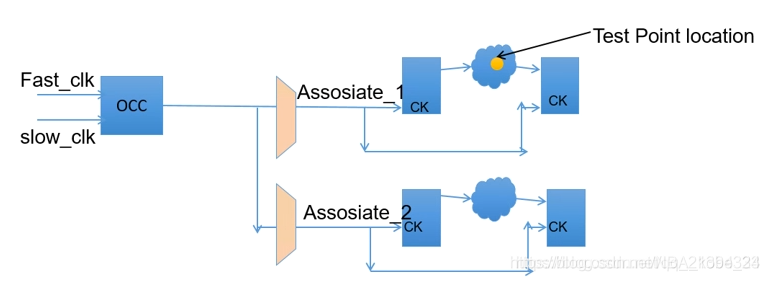

是的,Tool自动插DFT point,会把DFF 变成 scan-FF ,但组合逻辑深处,Tool就做不到了,因此有 DPPM(测试良率)和coverage(覆盖率)来评价DFT的质量。当Tool进行DFT后,如果coverage不够的话,就要手动插入 测试点,即 UDTP(user defined test point),它们用于增加DFT的coverage,在组合逻辑深度插入测试点。

如上所示,黄色点就是需要DFT之后,手动插入的测试点。那怎么来插入这个点呢?这便是接下来要学习、分析和讨论的问题。

在开始之前,有以下疑问,需要思考,以便更好的理解整个过程:

在手动插点的时候,我们怎么知道插在哪里?

最开始,以为是在跑完TMAX之后,看到coverage不够,就去研究代码,看哪些地方是关键路径,然后决定手动去插TP点;或者由designer提供需要插点的地方,毕竟designer了解他自己的code。但在RUN完TMAX之后,知道,Tool可以帮助提供 TP列表(来自tmax的fault中),因此,我们关注这些 TPs ,手动处理它们就行。

知道在哪里插点之后,更关键的问题是,怎么插?如下图,针对插点,需要添加一个DFF+MUX。它不同于SCAN-FF(先MUX选择,再DFF)。针对插点,需要提供 ck,MUX选择。插MUX之后,是会影响组合逻辑的时序的,要STA仔细检查。

————————————————

版权声明:本文为CSDN博主「时间看得见」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_21394333/article/details/111386124