吹吹水03FPGA前沿技术与ACAP-FPGA-Versal-ACAP-AI引擎-NoC片上网络

【吹吹水03】FPGA前沿技术与ACAP #FPGA #Versal ACAP #AI引擎 #NoC片上网络

吹水系列,概括一下FPGA的前沿技术,新时代应用和未来发展趋势,了解一下也好跟同事吹牛皮,其实没啥大用,闲着写写就当开拓思维了

1.FPGA前沿技术的创新方向

无论AMD与Intel两家巨头如何竞争创新,如何提出多么新颖的理念,它们的内在创新逻辑是一致的。这来源于新数字革命带来的新技术与新需求,因此在具体介绍两家最先进FPGA芯片之前,简单说明一下FPGA发展的趋势,这也便于我们理解这些创新的内在逻辑与未来可能的创新方向:

1.1 异构化

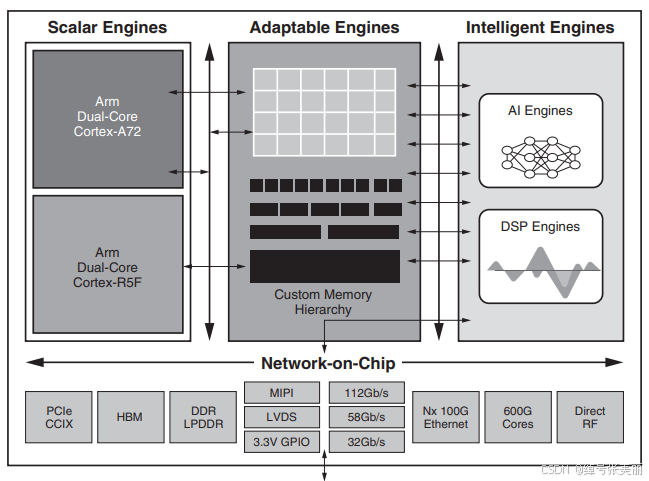

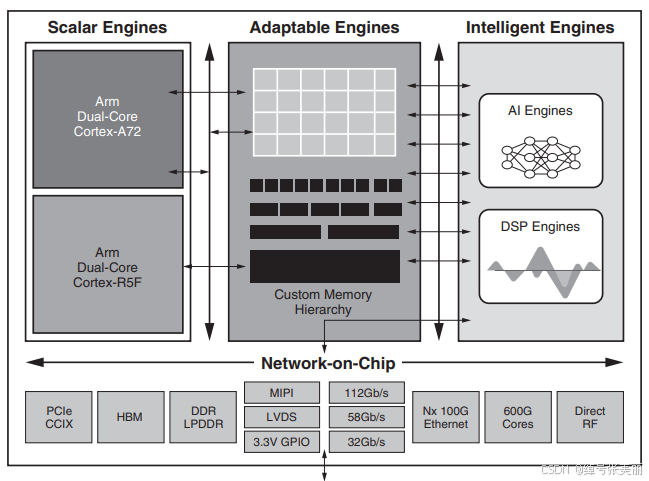

即将多种大型处理器,如CPU,NPU,FPGA,DSP,AI引擎等集成于一个片上系统的技术。这就要求FPGA集成多种处理器,具备与各式处理器高效协同工作的能力。如图所示为Versal ACAP芯片布局,可以看到这个系统集成了FPGA,DSP,AI引擎和其他处理器单元,FPGA通过NoC网络具备与其他处理器协同的能力。

1.2 AI加速

AI与机器学习的性能不仅依赖于软件算法模型,还依赖于执行其算法的硬件设备,通过硬件优化AI性能就是所谓的AI加速技术。FPGA在AI加速中具备得天独厚的优势,是极为理想的选择。如上图,许多高级FPGA已经集成了专用AI引擎,促进AI技术的发展与应用。

1.3 高速接口的适配

数据已然成为当今时代的核心资源,数据密集型产业(如数据中心、云计算、5G网络等)迭代需求前所未有,因此不断会有更先进的接口技术问世。FPGA需要及时跟进,集成更多更好的高速互联和接口标准。例如PCIe接口已经迭代到了PCIe6.0版本,其传输速率高至64GT/s,是一般FPGA(如Xilinx-K7)支持的PCIe2.0版本速率的十几倍;再如CCIX,HBM等等接口亦需要及时跟进。如上图ACAP也集成了多类接口。

1.4 设计自动化与高层次综合(HLS)

FPGA不断创新的同时,也使得其开发难度越来越大,为了降低开发难度与开发成本,FPGA行业对开发工具也需要及时创新。

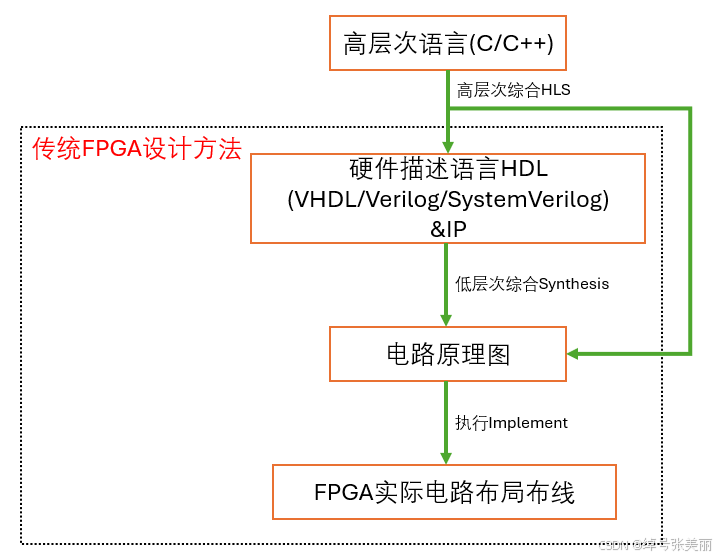

纵观FPGA发展史,就是设计自动化不断发展的历史,从最初的“手搭电路”,到利用HDL编程语言描述电路,再到复杂模块IP化,现今开发工具提出了简化设计难度的新方法——高层次综合(HLS,High-Level Synthesis).

如图,传统的FPGA设计方法以HDL语言与IP例化为核心,借助EDA工具完成Synthesis 和Implement的工作,从而完成从代码到硬件实现的工作。若想要使用C/C++语言完成硬件设计,则需要HLS工具,将其映射到HDL语言上或是直接生成电路原理图,从而进一步完成FPGA硬件的实现。现形的HLS工具已走出萌芽期,HLS技术已集成进了AMD的Vitis和Intel的Quartus Pro中去了。

2.Versal ACAP-FPGA异构的集大成者

ACAP(Adaptive Compute Acceleration Platform),即“自适应计算加速平台”,是Xilinx于2018年发布的一种新式芯片架构。它并非简单的FPGA,而是将 硬件可编程 处理器(FPGA), 软件可编程 处理器和软件可编程 加速引擎 结合为一体的高性能计算平台。Versal ACAP芯片就是Xilinx的代表性高性能处理器。

2.1 Versal ACAP芯片架构

如图所示,Versal ACAP芯片是FPGA异构化趋势的典型代表。该芯片基于7nm工艺制造,采用SSI技术(3D-FPGA技术,上一章有详细介绍),集成了FPGA,DSP,AI引擎,ARM这些可编程大型处理器,也包含了各类高速接口,存储器等资源。其特点如下:

2.2 可编程大型处理器

AI引擎:专为加速AI和机器学习任务设计的可编程设计模块。其包含高性能的矢量处理单元,能够执行深度学习推理、信号处理和数据分析等复杂计算任务,特别适用于深度神经网络的推理和训练,提供高吞吐量和低延迟的计算能力。

FPGA:这个就不多说了

DSP:专门用于高效执行数学运算和信号处理任务,如快速傅里叶变换(FFT)、滤波、卷积等,应用于通信系统、视频处理和科学计算中。

片上处理系统:包括一个或多个ARM处理器核心,用于执行软件任务、管理系统资源和控制数据流。

2.3 Network-on-Chip片上网络——各部分协同工作的桥梁

NoC负责在芯片内部不同模块之间传输数据。它通过多个 并行路径 实现高效的数据通信,减少了总线架构中的瓶颈问题。ACAP将数据处理与数据传输两种功能独立,让NoC专门负责数据传输,简化了设计,缓解了各部分及系统的布局布线压力。

2.4 开发方式

开发ACAP芯片涉及多个步骤和技术工具,在传统的FPGA开发方式基础上,还需要掌握新型的FPGA开发技术,其中AMD新开发工具Vitis尤为重要。

Vitis是Xilinx的统一开发环境,支持从嵌入式软件到加速应用的开发。开发者可以在Vitis中设计、编译和调试各部分芯片,同时支持高层次综合(HLS)和低层次的硬件描述。

- Vitis HLS

- 对于希望使用C/C++进行高层次综合(HLS)的开发者,Vitis HLS允许从高级语言生成硬件模块。这简化了复杂硬件的设计过程,使软件工程师也能参与硬件加速器的开发。

- Vitis AI

- 这是专为AI开发者设计的工具,支持在ACAP上加速AI推理任务。开发者可以利用Vitis AI库将预训练的AI模型部署到ACAP的AI引擎中。

3.总结&预告

这一章我们探讨了FPGA技术的前沿创新方向及其在现代计算中的应用,特别聚焦于AMD代表性产品-Versal ACAP芯片。我们首先讨论了FPGA的四大创新方向:异构化、AI加速、高速接口的适配、以及设计自动化与高层次综合(HLS)。这些趋势揭示了FPGA在满足新数字革命带来的需求方面的演变。接着,文章深入介绍了Versal ACAP芯片。通过集成多种可编程处理器和AI引擎,以及采用片上网络(NoC)技术,Versal ACAP展现出极高的性能和灵活性。文中详细描述了Versal ACAP的芯片架构、各处理单元的功能,以及NoC在数据传输中的重要性。最后,简单介绍了开发ACAP芯片的方法,尤其强调了AMD的Vitis开发工具的重要性,涵盖了Vitis HLS和Vitis AI在硬件加速与AI应用开发中的作用。这些工具使得开发者能够更高效地进行ACAP芯片的设计和优化。总体而言,文章从宏观趋势到具体产品,再到开发工具,为读者全面展示了FPGA技术的前沿发展和应用场景。

下一章我们着重说一下FPGA发展趋势对未来FPGA从业者的影响和新的要求。