AD9364-测试平台开发第五篇,ADCDAC接口

目录

AD9364 测试平台开发——第五篇,ADC/DAC接口

AD9364 测试平台开发——第五篇,ADC/DAC接口

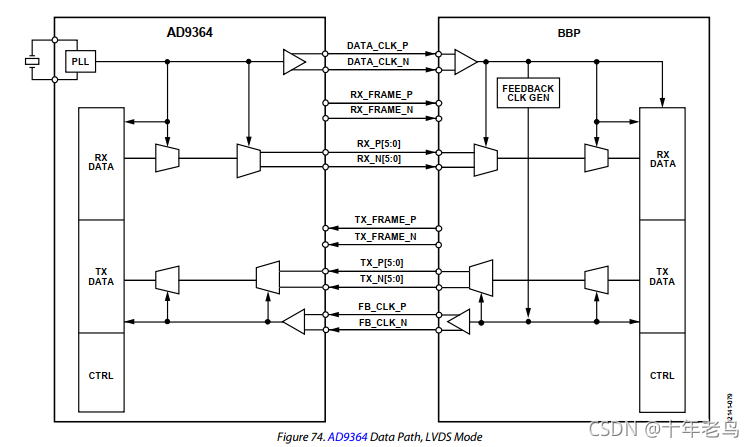

接口说明

采用AD9364接收的差分时钟[DATA_CLK_P/ DATA_CLK_N]作为时钟源,衍生出同频单端时钟iddr_clk,用于接收差分信号。衍生出同频单端时钟oddr_clk,作为发射差分信号时钟源,衍生出半频sample_clk信号用于信号处理

本工程中Iddr_clk 和oddr_clk 为40MHz;Sample_clk为20MHz

软件配置说明

生成脚本后,将脚本转化为本工程所需的串口总线模式即可。(这点后面再说)

ADC/DAC FPGA实现框图

注意:iddr_clk或者oddr_clk 的时钟相位要配合着 SPI指令来调准

首先要通过AD9364模块的自检指令确定ADC/DAC接口没有时序问题,再进行信号测试。

参考AD9361 BIST FAQ.pdf文档 总结了如下可以设置的测试项(指令),对ADC/DAC接口进行测试:

发射9361内部正弦波

发射9361内部伪随机码

接收9361内部正弦波

接收9361内部伪随机码(可观测误码发生次数)

发射FPGA生成的直流

发射FPGA生成的线性增加数

发射FPGA生成伪随机码

发射FPGA生成的正弦波

回环测试_回环直流

回环测试_回环线性增加数

回环测试_回环伪随机码(可观测误码发生次数)

回环测试_回环正弦波

这些测试项后面再详细列出实现指令