数字后端版图必备TapCell预防Latchup栓锁效应附对应版图画法

数字后端版图必备!TapCell预防Latchup栓锁效应(附对应版图画法)

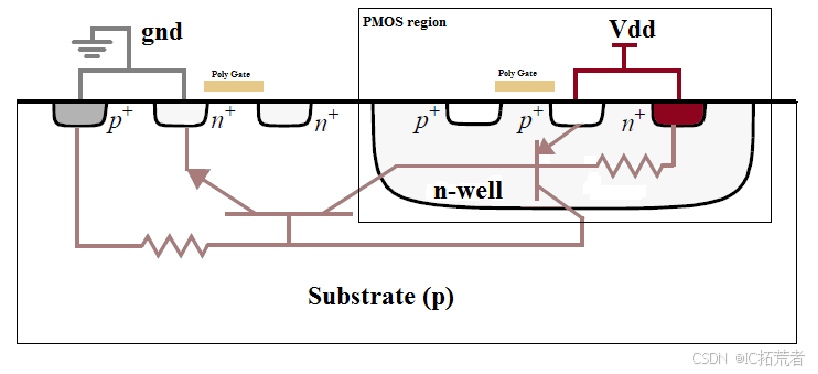

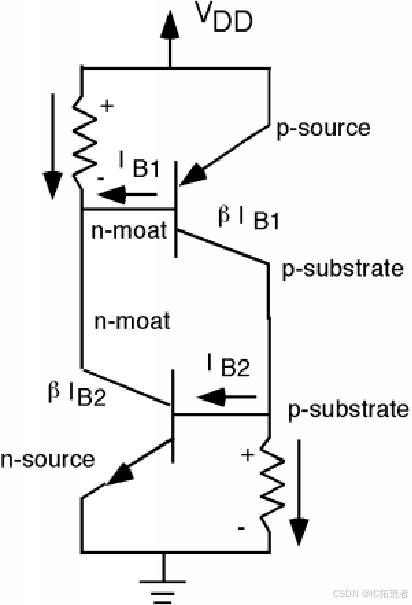

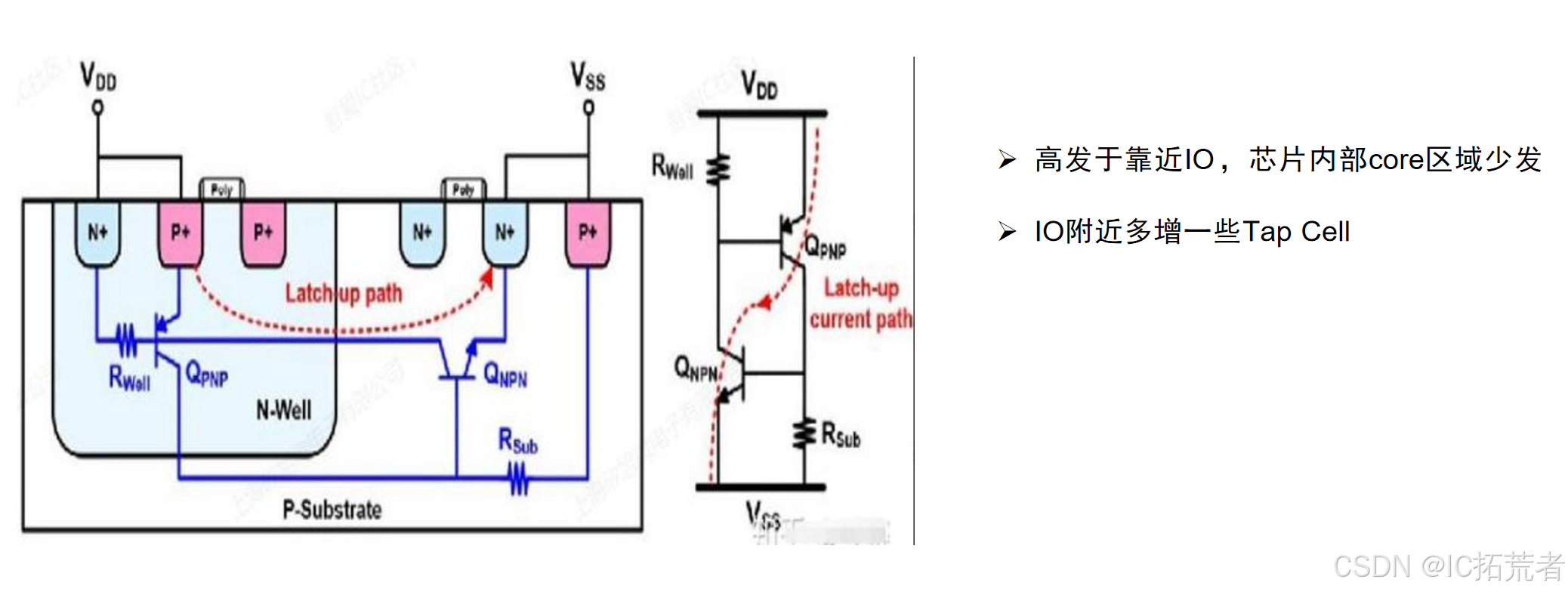

Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流。

Latchup栓锁效应原理:

Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路。

Latch-up发生的条件:

(i)当两个BJT都导通,在VDD和GND之间产生低阻抗通路;

(ii) 两个晶体管反馈回路(feedback loop)增益的乘积大于1

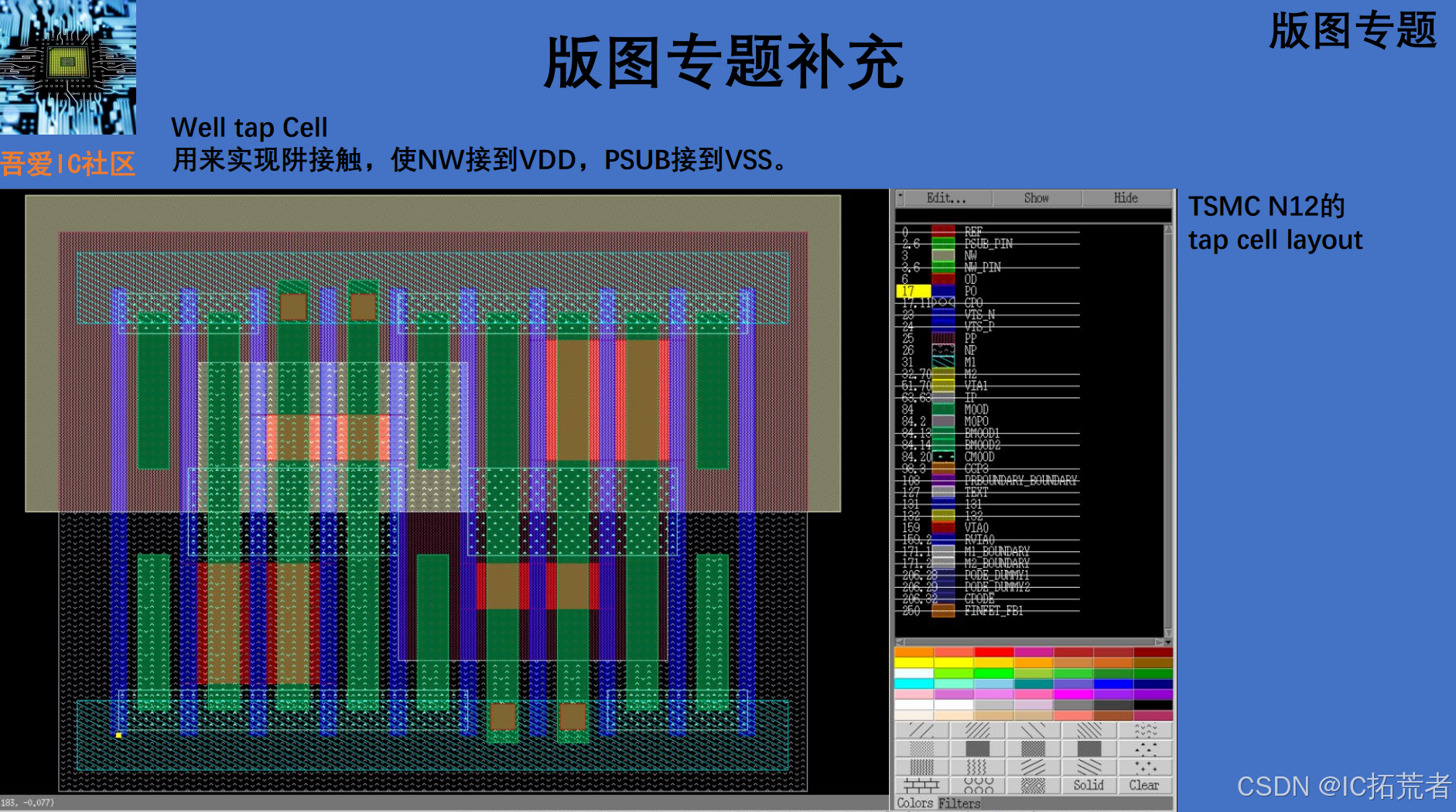

Well Tap Cell作用:

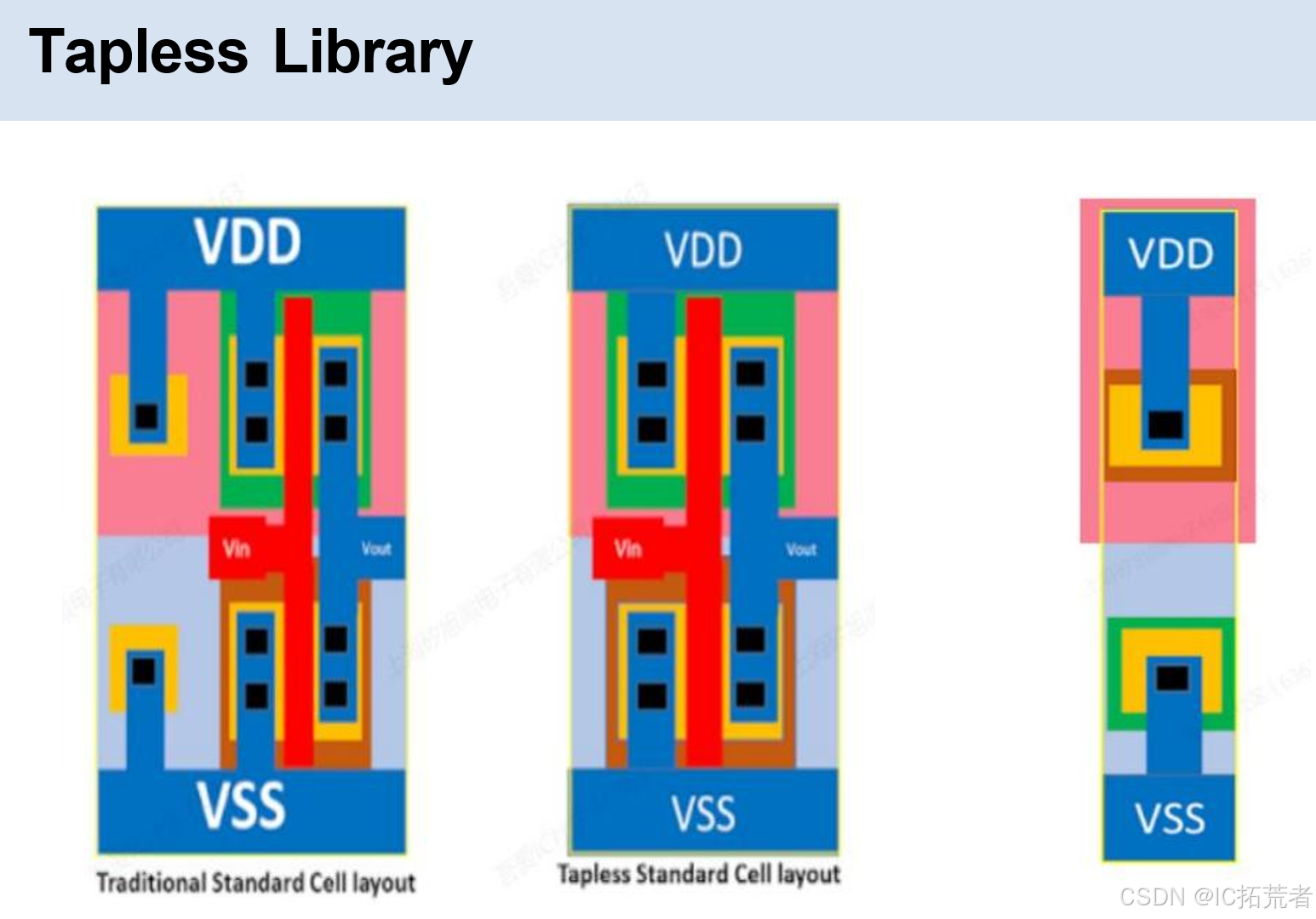

用来实现阱接触,使NW接到VDD,PSUB接到VSS!现在主流工艺都是使用tapless的标准单元库。因此在数字IC后端floorplan阶段都需要按照foundary规定的间距要求摆放tapcell。否则就会有latchup,同时calibre DRC检查也会报LUP.6的DRC Violation。

Well Tap Cell版图:

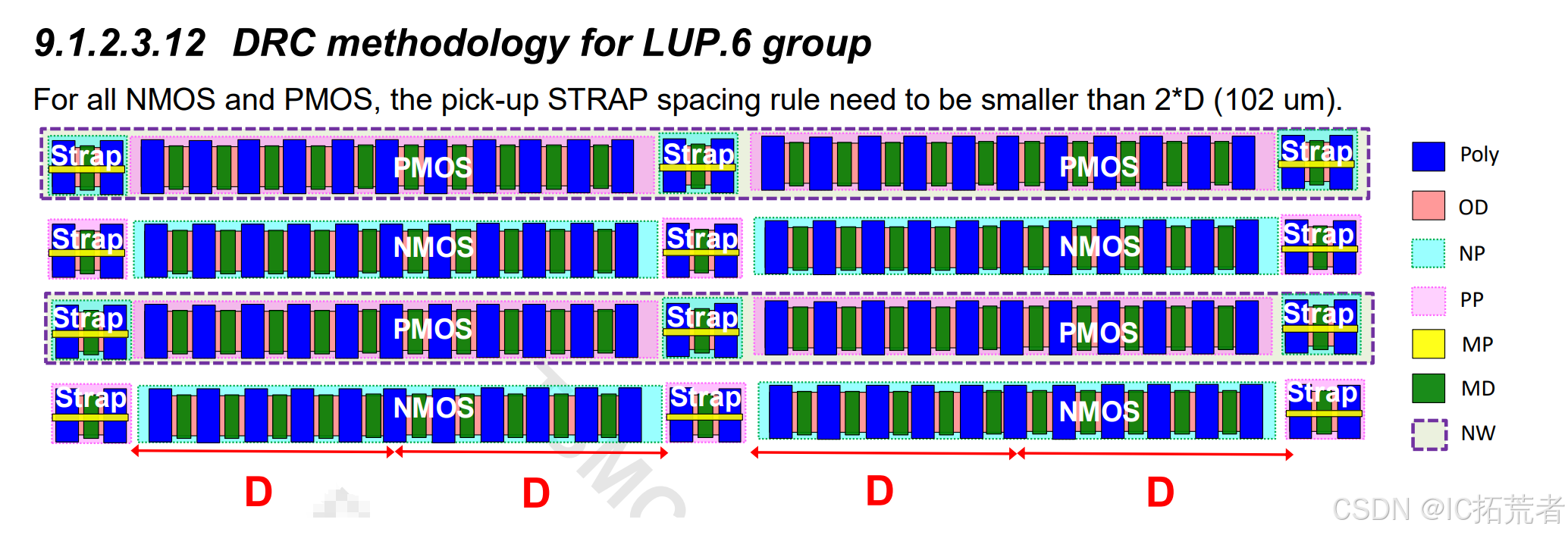

Well Tap Cell摆放原则:

需要严格按照foundary规定的间距要求来添加tapcell,否则在物理验证calibre drc检查阶段会查出Latch up drc violation。

这个要求可以确保NWELL和PSUB的电阻足够小,确保它们的电位分别接近于VDD和VSS,从而避免寄生三极管带来的栓锁效应。

Well Tap实现技巧:

1)NW->NP->contact(CO or M0OD)->M1 metal (VDD)构成NWELL tap

2)PSUB -> PP -> contact(CO or M0OD)->M1 metal (VSS)构成PWELL tap

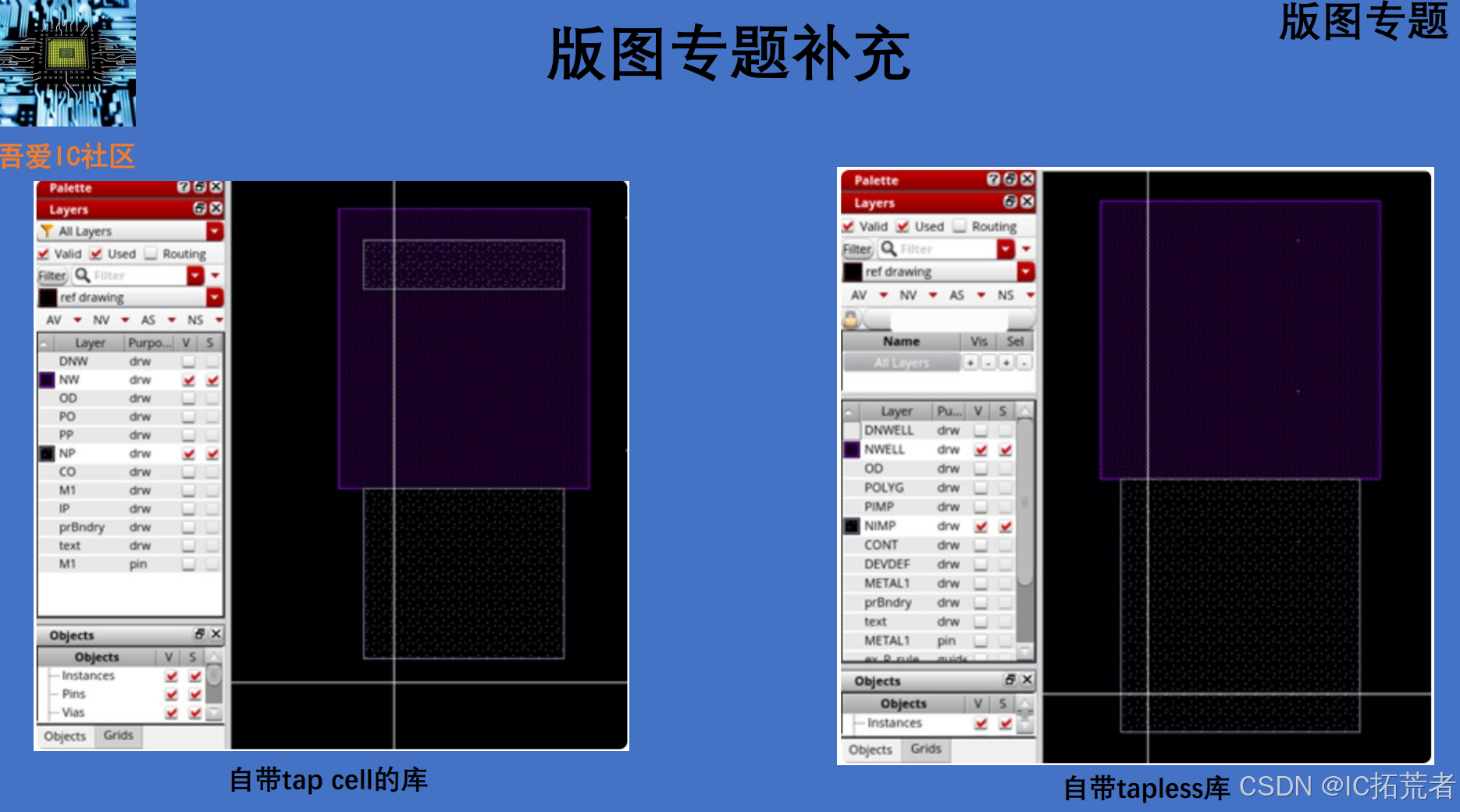

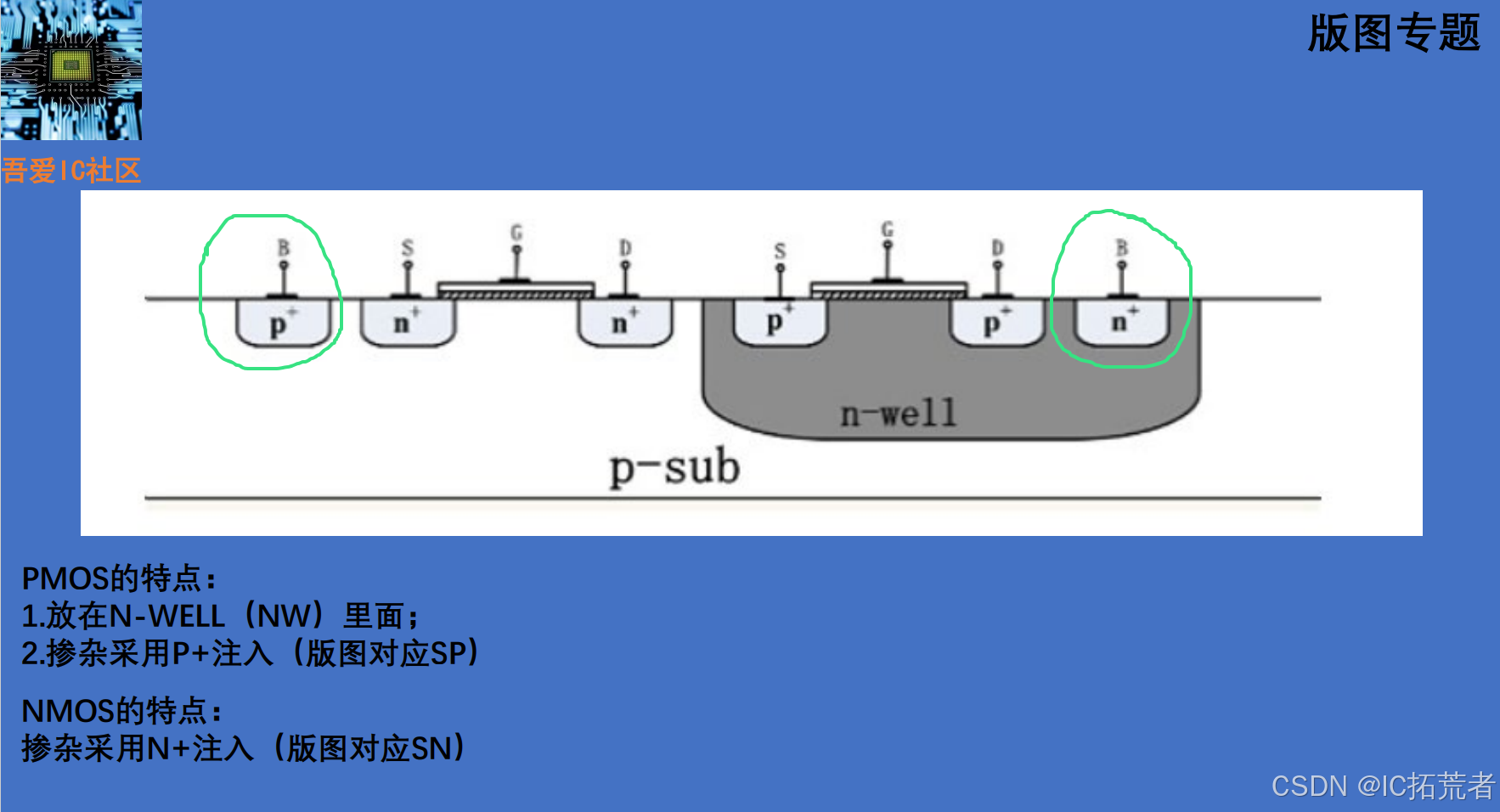

如何判断一个库是否是tapless?

只打开NW和NP,看看有没有重叠,没有重叠就是tapless库,有重叠则表示自带tap cell,不需要在PR的时候再添加tap cell。